描述

內容簡介

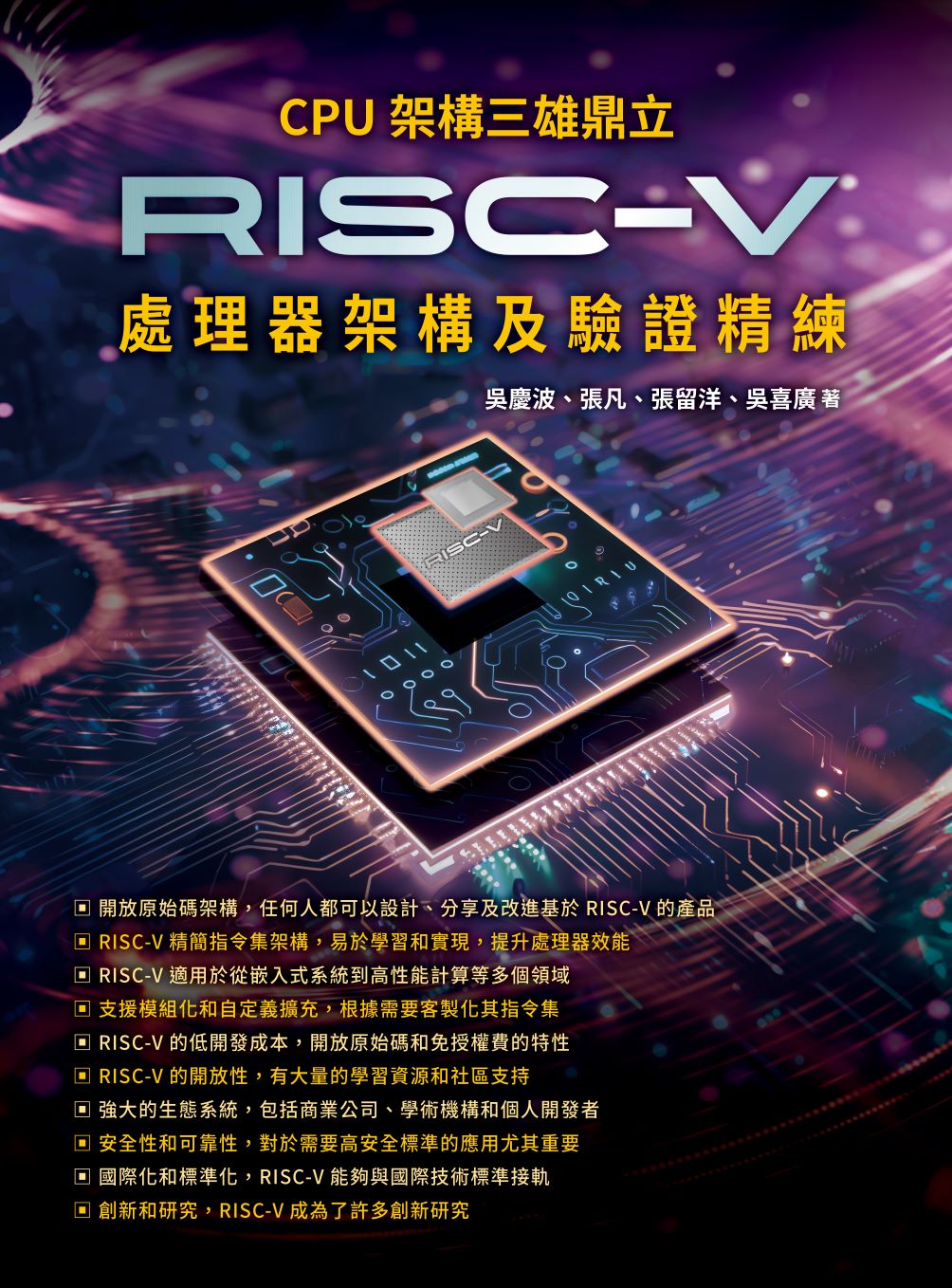

| ★開放原始碼架構,任何人都可以設計、分享及改進基於RISC-V的產品

★RISC-V精簡指令集架構,易於學習和實現,提升處理器效能 ★RISC-V適用於從嵌入式系統到高性能計算等多個領域 ★支援模組化和自定義擴充,根據需要客製化其指令集 ★RISC-V的低開發成本,開放原始碼和免授權費的特性 ★RISC-V的開放性,有大量的學習資源和社區支持 ★強大的生態系統,包括商業公司、學術機構和個人開發者 ★安全性和可靠性,對於需要高安全標準的應用尤其重要 ★國際化和標準化,RISC-V能夠與國際技術標準接軌 ★創新和研究,RISC-V成為了許多創新研究 有了封閉的Windows和MacOS,就有對應自由開放的Linux,而以民主自洽的作業系統生態中,竟然發展出比封閉架構更奔放的世界,如各式各樣的Linux Distros以及全世界市佔率最高的OS:Android。那邊在CPU的世界中呢?封閉的X86及高授權費用的ARM總是讓人綁手綁腳,但RISC-V的出現,讓CPU世界也能享有開放原始碼的自由。開放原始碼和免費使用是RISC-V最大的優勢之一。這不僅讓開發者能夠針對特定的應用場景進行定制和優化,降低了CPU的設計成本,也促進了技術的創新和發展。RISC-V的模組化和簡潔設計更是一大亮點,使得晶片設計者能夠輕易地開發出簡單、高效的RISC-V CPU,尤其適合於對功耗和程式體積有嚴格要求的嵌入式和物聯網領域。自2015年RISC-V基金會成立以來,它已成為一個開放、協作的軟硬體創新者社區,不僅指導著RISC-V的未來發展方向,也推動了其在全球範圍內的廣泛應用。越來越多的產業巨頭加入了RISC-V基金會,如果你想熟悉一個CPU架構,又想自己實作出來,RISC-V將會是你最棒的選擇。 |

作者簡介

|

目錄

| 第一部分 處理器指令集架構

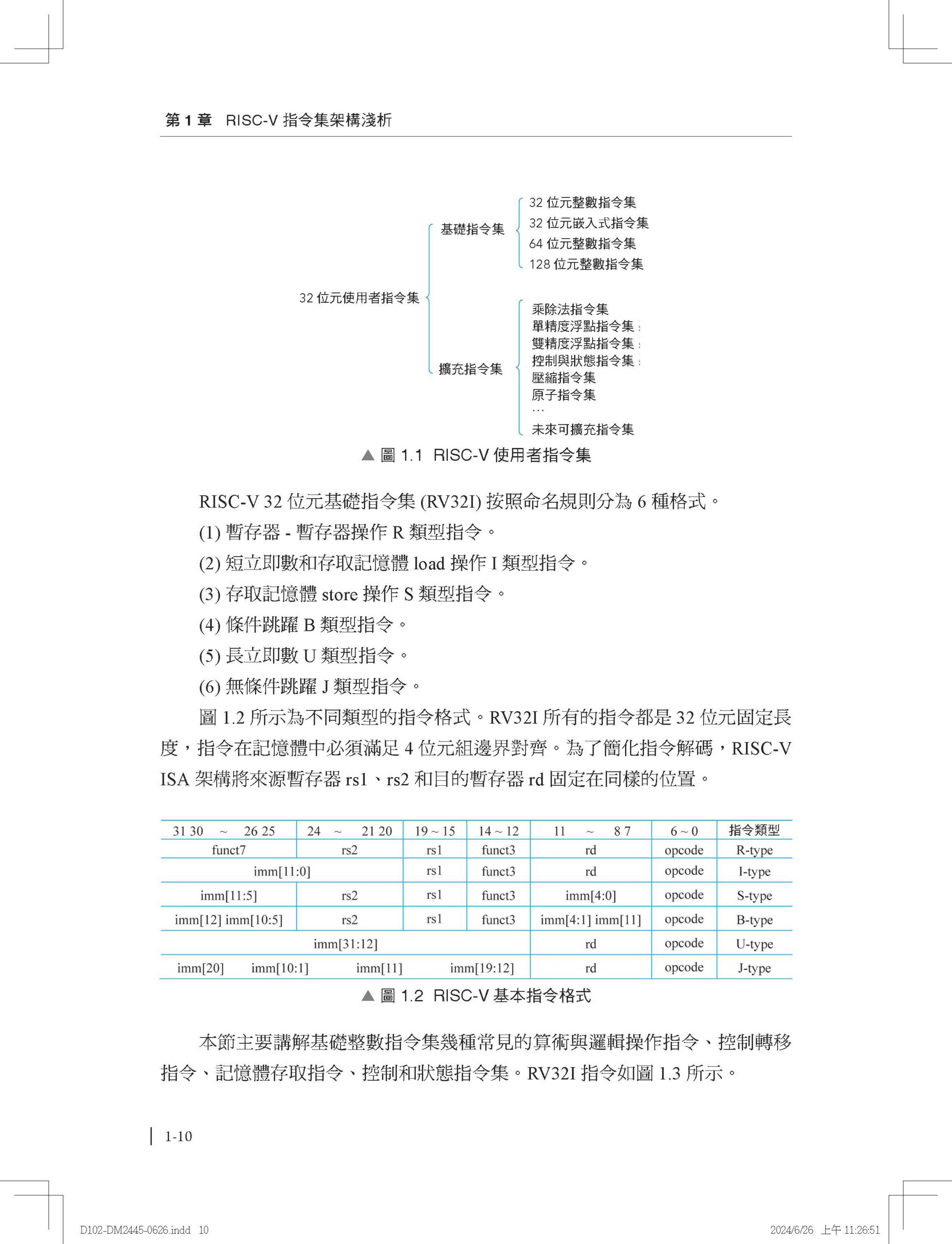

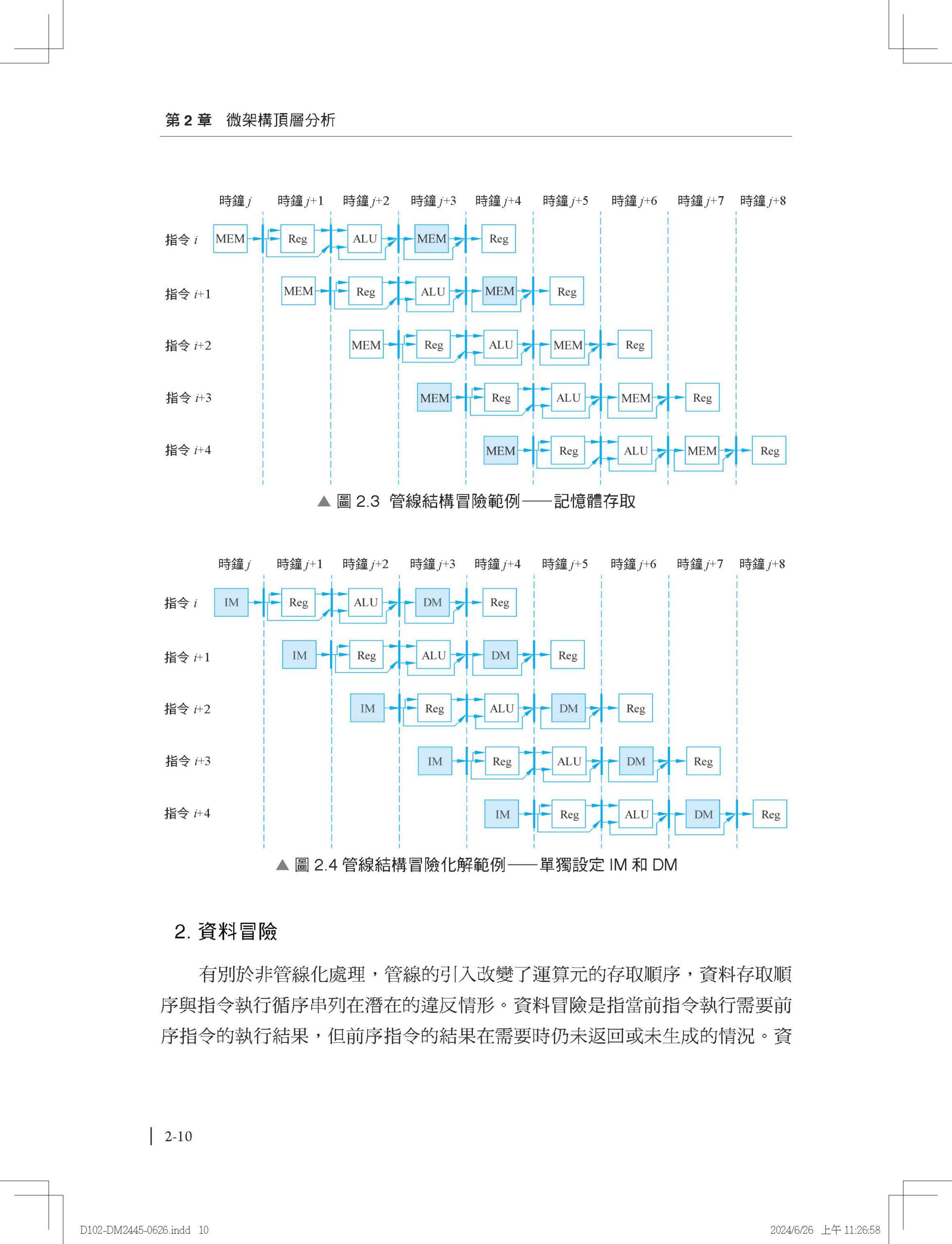

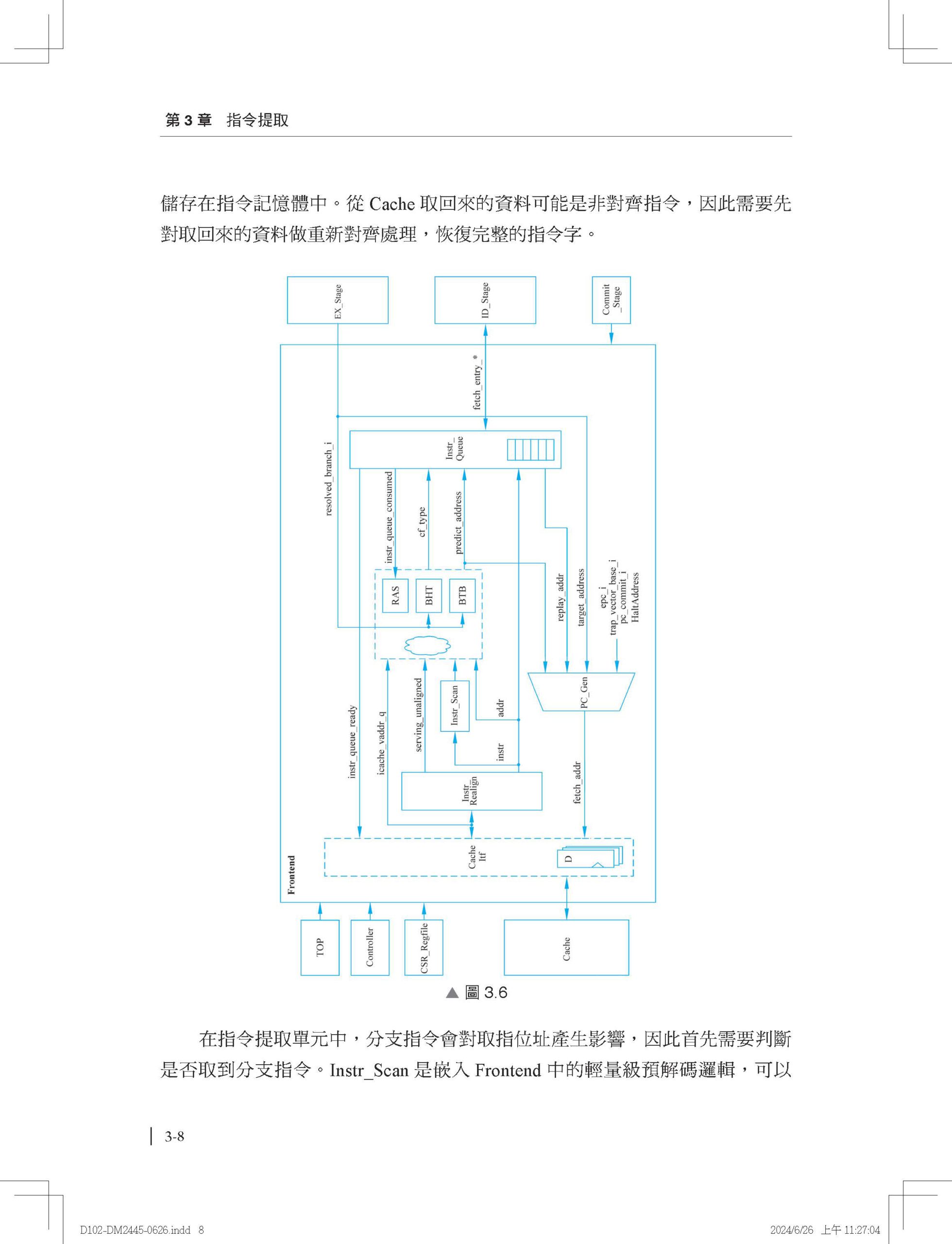

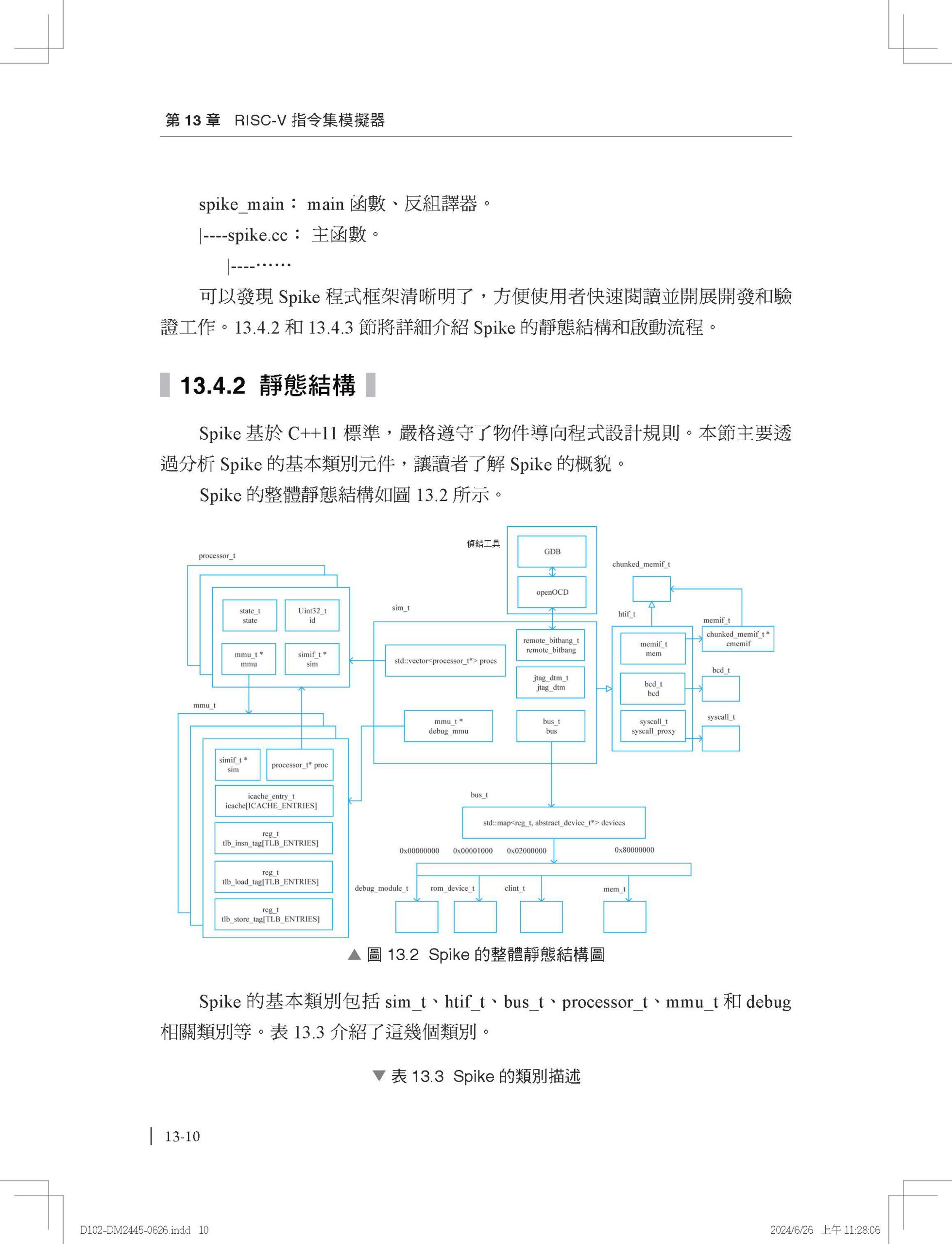

第1章 RISC-V 指令集架構淺析 1.1指令集架構 1.2 RISC-V 指令集簡介 1.3 RISC-V 基礎指令集 1.4 RISC-V 擴展指令集 1.5 RISC-V 64位元基礎指令 1.6 RISC-V 特權指令 1.7 本章小結 第二部分 處理器微架構 第2章 微架構頂層分析 2.1 管線 2.2 Ariane微架構 2.3 本章小結 第3章 指令提取 3.1 指令提取概述 3.2分支預測演算法 3.3 指令提取單元設計 3.4 本章小結 第4章 指令解碼 4.1指令解碼概述 4.2指令解碼單元設計 4.3本章小結 第5章 指令發射 5.1單發射和多發射 5.2 順序發射和亂序發射 5.3指令動態排程 5.4指令發射單元設計 5.5本章小結 第6章 指令執行 6.1指令執行敘述 6.2 指令執行單元設計 6.3 本章小結 第7章 指令提交 7.1 指令提交概述 7.2指令提交單元設計 7.3本章小結 第8章 儲存管理 8.1 快取原理 8.2快取設計 8.3儲存管理部件 8.4儲存管理部件設計 8.5本章小結 第9章 中斷和異常 9.1中斷和異常概述 9.2異常處理機制 9.3中斷控制平臺 9.4中斷和異常設計實例 9.5本章小結 第三部分 處理器驗證 第10章 UVM 簡介 10.1 UVM 概述 10.2 UVM 基本概念 10.3 UVM 組件介紹 10.4 本章小結 第11章 RISC-V 驗證框架 11.1通用驗證框架 11.2 RISC-V 驗證特點 11.3本章小結 第12章 RISC-V 指令發生器 12.1 RISCV-DV 概述 12.2 RISCV-DV 使用方法 12.3 RISCV-DV 結構分析 12.4本章小結 第13章 RISC-V 指令集模擬器 13.1 RISC-V 指令集模擬器概述 13.2 Spike概述 13.3 Spike使用方法 13.4 Spike原始程式分碼析 13.5 Spike擴展 13.6本章小結 |

序

| 前 言

RISC-V 是基於精簡指令原則的開放原始碼指令集架構。該項目2010年始於加州大學伯克利分校,採用開放原始碼BSDLicense。RISC-V 指令集可自由地用於任何目的,允許任何人設計、製造、銷售RISC-V 晶片和軟體,而不必支付給任何公司專利費。其目標是成為一個通用的指令集架構,能適應包括從最袖珍的嵌入式控制器到最快的高性能電腦等各種規模的處理器。與現有其他指令集架構相比,RISC-V 架構有著鮮明的特點和優勢。 開放原始碼和免費。開放原始碼表示開發者可以針對特定應用場景進行訂製最佳化,免費表示RISC-V 可以幫助開發者有效降低 CPU 設計成本。 模組化和簡潔。模組化設計和簡潔的基礎指令可以讓使用 RISC-V 技術的晶片設計者開發出很簡單的RISC-VCPU,特別是在嵌入式和物聯網(Internet of Things,IoT)等領域對功耗和程式體積有較高限制的應用場景。 靈活和可擴展性。RISC-V 架構預留大量的編碼空間用於自訂擴展,並定義了4行使用者指令供使用者直接使用,該特性在安全或IoT領域有著廣泛的需求。 2015年,RISC-V 基金會成立,它是開放、協作的軟硬體創新者社區,指導未來發展方向並推動RISC-V 的廣泛應用。 雖然RISC-V 目前的生態還處於初級階段,但是越來越多的產業界巨頭對 RISC-V有著強烈的興趣並紛紛加入RISC-V 基金會,RISC-V 極有可能像Linux那樣開啟開放原始碼晶片設計的黃金時代。從自主可控生態建設來看,從零開始建立互相相容的 RISC-V 生態當下也許是最好的時機,可以期待在不久的將來,RISC-V 的生態就可以挑戰x86和 ARM 的地位。 全書由13章組成,分為三大部分。第1章為第一部分———處理器指令集架構,主要介紹指令集相關基礎概念及 RISC-V 指令集架構。第2~9 章為第二部分———處理器微架構,主要內容為RISC-V CPU 微架構設計及邏輯實現,從微架構和管線設計原理著手,詳細介紹 RISC-V 指令集架構 CPU 的設計方法,並以開放原始碼處理器核心 Ariane 為例,介紹 RISC-V 處理器的實現細節。第10~13 章為第三部分———處理器驗證,主要內容為RISC-VCPU 驗證,著重介紹如何基於當前主流驗證方法UVM 建構RISC-VCPU驗證平臺,並完成 CPU 核心的驗證工作。 希望本書能夠成為RISC-V 處理器同好的入門圖書,為RISC-V 處理器在國內的普及和發展貢獻綿薄之力。 感謝鵬城實驗室自主可控專案小組參與本書撰寫的所有成員,撰寫過程中有著大量的程式分析、資料整理和文稿校對工作,他們的付出使得本書能夠最終成文。同時,還要感謝清華大學出版社各位編輯的大力支持,他們認真細緻的工作保證了本書的品質。 由於編者水準有限,書中難免有疏漏和不足之處,懇請讀者批評指正!

編 者 |